Pós-Graduação em Ciência da Computação

## FORMALISATION OF SYSML DESIGN MODELS AND AN ANALYSIS STRATEGY USING REFINEMENT

by

### Lucas Albertins de Lima

**PhD Thesis**

Universidade Federal de Pernambuco posgraduacao@cin.ufpe.br www.cin.ufpe.br/~posgraduacao

RECIFE/2016

### Lucas Albertins de Lima

## FORMALISATION OF SYSML DESIGN MODELS AND AN ANALYSIS STRATEGY USING REFINEMENT

A Ph.D. Thesis presented to the Centro de Informática of Universidade Federal de Pernambuco in partial fulfillment of the requirements for the degree of Philosophy Doctor in Computer Science.

Advisor: Juliano Manabu Iyoda

Co-Advisor: Augusto Cezar Alves Sampaio

#### Catalogação na fonte Bibliotecária Monick Raquel Silvestre da S. Portes, CRB4-1217

#### L732f Lima, Lucas Albertins de.

Formalisation of SysML design models and an analysis strategy using refinement / Lucas Albertins de Lima. – 2016.

298 f.: il., fig., tab.

Orientador: Juliano Manabu Iyoda.

Tese (Doutorado) – Universidade Federal de Pernambuco. CIn, Ciência da Computação, Recife, 2016.

Inclui referências e apêndices.

- 1. Engenharia de software. 2. Métodos formais. 3. Modelagem de sistemas.

- 4. Verificação de sistemas. I. Iyoda, Juliano Manabu. (orientador). II. Título.

005.1 CDD (23. ed.) UFPE- MEI 2016-057

### Lucas Albertins de Lima

### FORMALISATION OF SYSML DESIGN MODELS AND AN ANALYSIS STRATEGY USING REFINEMENT

Tese apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Federal de Pernambuco, como requisito parcial para a obtenção do título de **Doutor** em Ciência da Computação.

| o <b>f. Dr. Julia</b><br>ntador do Traba | no Manabu Iyoda<br>lho de Tese                                                                     |

|------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                          | BANCA EXAMINADORA                                                                                  |

|                                          | Prof. Dr. Paulo Henrique Monteiro Borba<br>Centro de Informática / UFPE                            |

| -                                        | Prof. Dr. Alexandre Cabral Mota<br>Centro de Informática / UFPE                                    |

| _                                        | Profa. Dra. Leopoldo Mota Teixeira<br>Centro de Informática / UFPE                                 |

| _<br>De                                  | Prof. Dr. Marcel Vinicius Medeiros Oliveira partamento de Informática e Matemática Aplicada / UFRN |

Laboratório Associado de Computação e Matemática Aplicada / INPE

### Acknowledgements

Primeiramente gostaria de agradecer a Deus por ter me proporcionado a realização deste trabalho e por ter me guiado durante toda esta jornada. Em seguida as pessoas mais importantes da minha vida, minha esposa Pâmela e meu filho William por todo o apoio, compreensão e momentos felizes que me ajudaram a seguir em frente. Também tenho muito a agradecer a meus pais José Nivaldo e Ana Maria por sempre acreditarem que eu posso dar mais um passo adiante e por estarem sempre ao meu lado dando força sempre que preciso. A toda a minha família por sempre me incentivarem desde de que me dou por gente, especialmente ao meu querido avô Urcicino cujo exemplo e perseverança nos encorajou a perseguir nossos sonhos.

Aos meus orientadores, Juliano Iyoda e Augusto Sampaio, por toda compreensão, dedicação e aconselhamentos que tornaram possível a concretização deste trabalho. À minha orientadora durante o doutorado sanduíche, Ana Cavalcanti, cujos direcionamentos foram cruciais para a conclusão da integração das semânticas e as estratégias de análise formal, além de ter me proporcionado uma experiência acadêmica inspiradora da qual tirei lições para o resto da minha vida.

Ao colega Alvaro Miyazawa que contribuiu na definição da semântica integrada dos diferentes diagramas, além de ter definido a semântica formal de máquinas de estado que usamos neste trabalho. Aos colegas André Didier e Márcio Cornélio por terem contribuído na definição da semântica formal de diagrama de atividades.

Ao projeto COMPASS por ter permitido o desenvolvimento desta pesquisa inserida num contexto acadêmico e industrial, além do apoio financeiro através da bolsa de estudos. Ter desenvolvido esta pesquisa com colegas de diferentes universidades e empresas estrangeiras foi extremamente enriquecedor para minha carreira.

Ao CNPq e ao projeto Ciência Sem Fronteiras pelo incentivo financeiro para realização do doutorado sanduiche na Universidade de York na Inglaterra.

Finalmente, ao projeto INES que financiou a participação nas diversas conferências onde publicamos artigos e a todos os colegas do programa de pós-graduação do Centro de Informática da UFPE.

### Resumo

O aumento da complexidade dos sistemas tem levado a um aumento na dificuldade da atividade de projeto. A abordagem padrão para desenvolvimento, baseada em tentativa e erro, com testes usados em estágios avançados para identificar erros, é custosa e leva a prazos de entrega imprevisíveis. Além disto, para sistemas críticos, para os quais segurança é um conceito chave, Verificação e Validação (V&V) com antecedência é reconhecida como uma abordagem valiosa para promover confiança. Neste contexto, nós identificamos três características importantes e desejáveis de uma técnica de V&V: (i) uma linguagem de modelagem gráfica; (ii) raciocínio formal e rigoroso, e (iii) suporte automático para modelagem e raciocínio.

Nós tratamos estes pontos com uma técnica de refinamento para SysML apoiada por ferramentas. SysML é uma linguagem baseada na UML para o projeto de sistemas. Ela tem se tornado um padrão *de facto* na área. Há uma grande disponibilidade de ferramentas de fornecedores como IBM, Atego, e Sparx Systems. Nosso trabalho se destaca de duas maneiras: ao fornecer uma semântica para refinamento e considerar uma coleção representativa de elementos do perfil UML4SysML (blocos, máquina de estados, atividades, e interações) usados de forma combinada. Nós fornecemos uma estratégia para analisar modelos de projeto especificados em SysML. Isto facilita a descoberta de problemas mais cedo durante o ciclo de vida de desenvolvimento de sistemas, reduzindo tempo e custos de produção.

Neste trabalho nós descrevemos nossa semântica a qual é definida usando uma álgebra de processo rica em estado chamada CML e implementada em uma ferramenta para geração automática de modelos formais. Nós também mostramos como esta semântica pode ser usada para análise baseada em refinamento. Nossos estudos de caso são um protocolo de eleição de líder, o qual é um componente crítico de uma aplicação industrial, e um sinal anão, o qual é um dispositivo para controlar tráfego em linhas férreas. Nossas contribuições são: um conjunto de orientações que fornecem significado para os diferentes elementos de modelagem de SysML usados durante o projeto de sistemas; as semânticas formais individuais para atividades, blocos e interações de SysML; uma semântica integrada que combina estas semânticas com outra definida para máquina de estados; e um arcabouço que usa refinamento para raciocínio de sistemas especificados por coleções de diagramas SysML.

**Palavras-chave:** Álgebra de processos. CML. CSP. refinamento. automação. SysML. semântica.

### **Abstract**

The increasing complexity of systems has led to increasing difficulty in design. The standard approach to development, based on trial and error, with testing used at later stages to identify errors, is costly and leads to unpredictable delivery times. In addition, for critical systems, for which safety is a major concern, early verification and validation (V&V) is recognised as a valuable approach to promote dependability. In this context, we identify three important and desirable features of a V&V technique: (i) a graphical modelling language; (ii) formal and rigorous reasoning, and (iii) automated support for modelling and reasoning.

We address these points with a refinement technique for SysML supported by tools. SysML is a UML-based language for systems design; it has itself become a *de facto* standard in the area. There is wide availability of tool support from vendors like IBM, Atego, and Sparx Systems. Our work is distinctive in two ways: a semantics for refinement and for a representative collection of elements from the UML4SysML profile (blocks, state machines, activities, and interactions) used in combination. We provide a means to analyse design models specified using SysML. This facilitates the discovery of problems earlier in the system development lifecycle, reducing time and costs of production.

In this work we describe our semantics, which is defined using a state-rich process algebra called CML and implemented in a tool for automatic generation of formal models. We also show how the semantics can be used for refinement-based analysis and development. Our case studies are a leadership-election protocol, a critical component of an industrial application, and a dwarf signal, a device used to control rail traffic. Our contributions are: a set of guidelines that provide meaning to the different modelling elements of SysML used during the design of systems; the individual formal semantics for SysML activities, blocks and interactions; an integrated semantics that combines these semantics with another defined for state machines; and a framework for reasoning using refinement about systems specified by collections of SysML diagrams.

**Keywords:** Process algebra. CML. CSP. refinement. Automation. SysML. Semantics.

## List of Figures

| 1.1  | The process of our approach                              | 21 |

|------|----------------------------------------------------------|----|

| 2.1  | Overview of the relationship between UML 2 and SysML     | 24 |

| 2.2  | SysML diagram taxonomy                                   | 25 |

| 2.3  | A block definition diagram                               | 26 |

| 2.4  | An example of an internal block diagram                  | 26 |

| 2.5  | A state machine diagram                                  | 27 |

| 2.6  | Example of an activity diagram                           | 29 |

| 2.7  | Control nodes                                            | 30 |

| 2.8  | Example of a sequence diagram                            | 31 |

| 2.9  | Example of a sequence diagram with <i>interactionUse</i> | 32 |

| 2.10 | Example of a sequence diagram with gates                 | 32 |

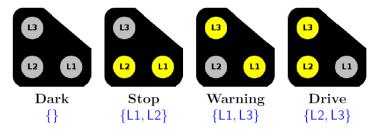

| 3.1  | An illustration of a dwarf signal                        | 16 |

| 3.2  | The proper states of a dwarf signal                      | 17 |

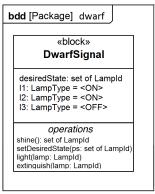

| 3.3  | The BDD of a dwarf signal                                | 17 |

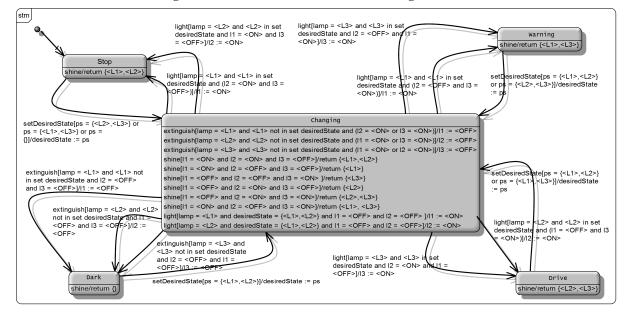

| 3.4  | The state machine of the <b>DwarfSignal</b> block        | 18 |

| 3.5  | Abstract model: block definition diagram                 | 19 |

| 3.6  | Abstract model: state machine diagram                    | 50 |

| 3.7  | Violation of guidelines of usage                         | 51 |

| 3.9  | Example of an activity diagram                           | 52 |

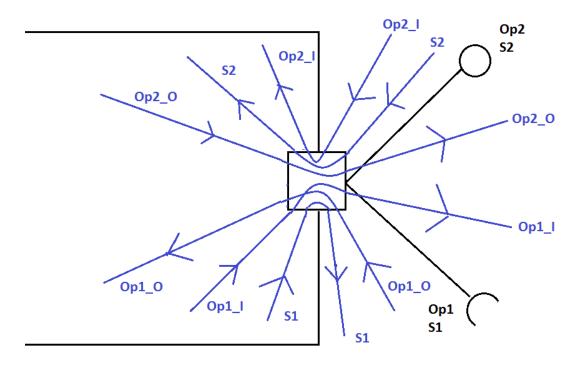

| 4.1  | Communication channels for blocks                        | 51 |

| 4.2  | Allowed communication patterns for a port                | 53 |

| 4.3  | Processes of a simple block                              | 73 |

| 5.1  | Overview of the model of state machines                  | 9  |

| 5.2  | Overview of the representation of activities in CML      | )2 |

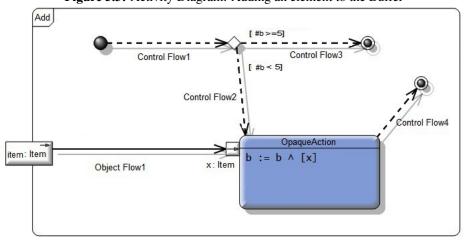

| 5.3  | Activity Diagram: Adding an element to the Buffer        | )3 |

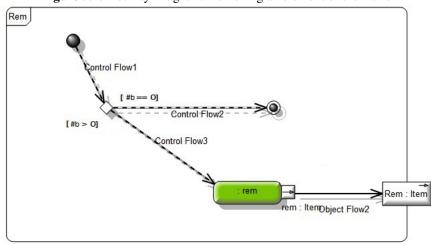

| 5.4  | Activity Diagram: Removing an element of the Buffer      | )4 |

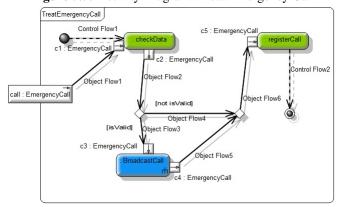

| 5.5  | Activity Diagram: Treat Emergency Call                   | )4 |

| 5.6  | Activity Diagram: Broadcasting a Call                    | )5 |

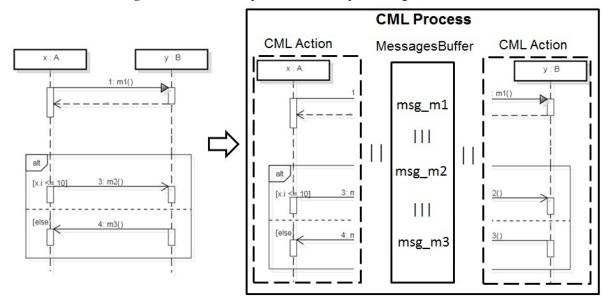

| 6.1  | Semantic representation of sequence diagrams in CML      | 20 |

| 6.2  | Illustration of a lifeline                               | 24 |

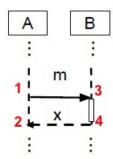

| 6.3  | Illustration of a synchronous message                    | 26 |

| 6.4  | Illustration of an asynchronous message                  | 28 |

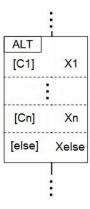

| 6.5  | Illustration of an alternative combined fragment for a lifeline     | 129 |

|------|---------------------------------------------------------------------|-----|

| 6.6  | Illustration of a state invariant                                   | 131 |

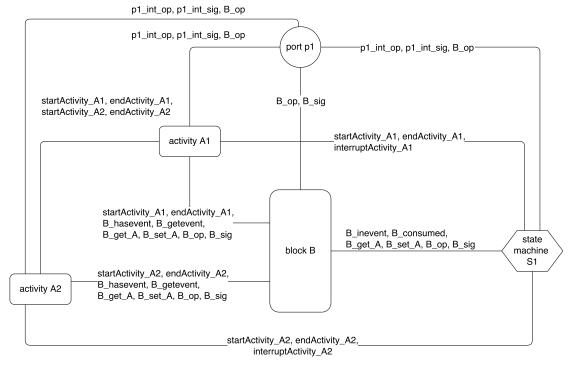

| 7.1  |                                                                     | 137 |

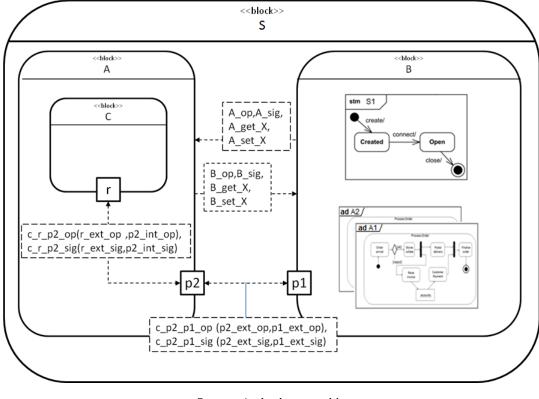

| 7.2  | Overview of the communication between the models of multiple blocks | 142 |

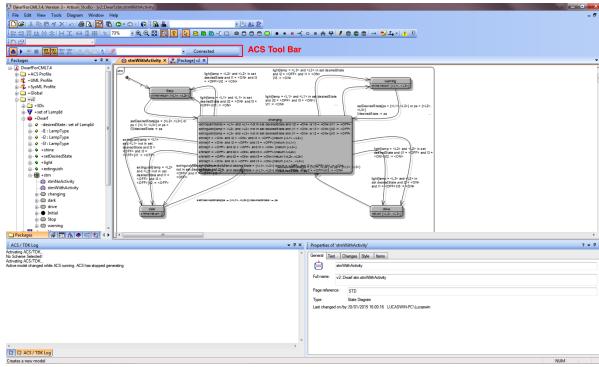

| 8.1  | Artisan Studio: ACS tool bar                                        | 151 |

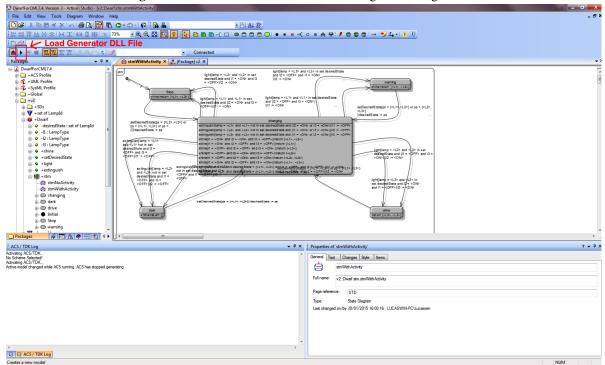

| 8.2  | Artisan Studio: Button for loading the CML generator                | 151 |

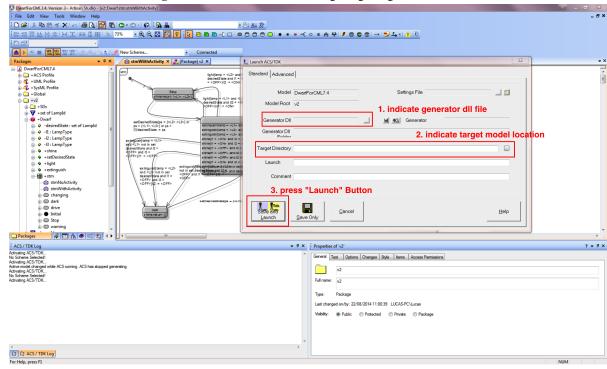

| 8.3  | Artisan Studio: Configuring the generator DLL                       | 152 |

| 8.4  | Artisan Studio: Status of the generation process                    | 152 |

| 8.5  | Animation in Symphony: selecting an event                           | 154 |

| 8.6  | Animation in Symphony: executing a valid event                      | 154 |

| 8.7  | Animation in Symphony: executing an invalid event                   | 155 |

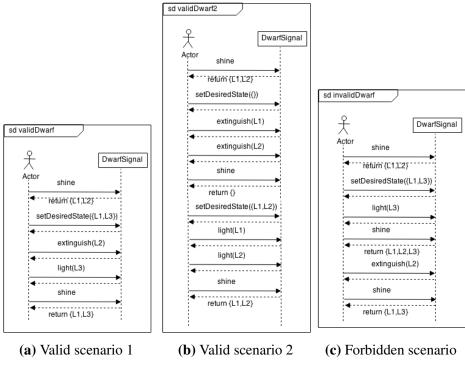

| 8.8  | Sequence diagram examples                                           | 157 |

| 8.10 | Work flow of the analysis of properties                             | 159 |

| 8.11 | The ActShine activity                                               | 161 |

| 8.12 | Sequence diagram examples of the Dwarf Signal system                | 162 |

| 8.14 | Refinement statement with optimisations for FDR                     | 163 |

| 8.15 | Example of refinement for inserting a private operation             | 166 |

| 8.16 | Example of refinement for inserting a private attribute             | 167 |

| 8.17 | Example of refinement for decomposing a block (part 1)              | 168 |

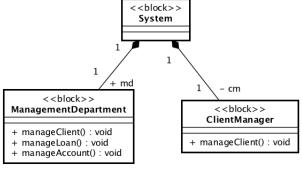

| 8.18 | Block diagrams of the ManagementDepartment system v1                | 169 |

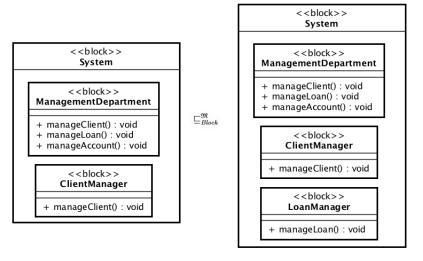

| 8.20 | Example of refinement for decomposing a block (part 2)              | 169 |

| 8.21 | Example of refinement for decomposing a block (part 3)              | 170 |

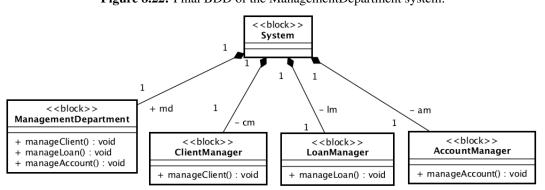

| 8.22 | Final BDD of the ManagementDepartment system                        | 170 |

| 8.23 | Final IBD of the ManagementDepartment system                        | 170 |

| B.1  | Procedures for pre-processing the CML model                         | 239 |

### List of Tables

| 3.1 | Main semantic functions for SysML models                                   | 55  |

|-----|----------------------------------------------------------------------------|-----|

| 3.2 | SysML-CML correspondence                                                   | 59  |

| 4.1 | Coverage comparison                                                        | 97  |

| 5.1 | Coverage comparison                                                        | 117 |

| 6.1 | Coverage comparison                                                        | 135 |

| 7.1 | Summary of related works                                                   | 147 |

| 8.1 | Specifications of the computer used in the evaluation                      | 164 |

| 8.2 | Results of the scalability evaluation                                      | 165 |

| B.1 | Mapping between CML and CSP functions for manipulating sequences and sets. | 250 |

### Contents

| 1 | Intr | oduction                                  | 16 |

|---|------|-------------------------------------------|----|

|   | 1.1  | Structure of the Thesis                   | 21 |

| 2 | Bac  | kground                                   | 23 |

|   | 2.1  | SysML                                     | 23 |

|   |      | 2.1.1 Block-definition diagram            | 25 |

|   |      | 2.1.2 Internal block diagram              | 26 |

|   |      | 2.1.3 State-machine diagram               | 27 |

|   |      | 2.1.4 Activity diagram                    | 29 |

|   |      | 2.1.5 Sequence diagram                    | 30 |

|   |      | 2.1.6 Final Remarks on SysML models       | 33 |

|   | 2.2  | CML                                       | 33 |

|   | 2.3  | Final Remarks                             | 39 |

| 3 | Mod  | delling Patterns                          | 40 |

|   | 3.1  | Guidelines of usage                       | 40 |

|   |      | 3.1.1 Entity definition guidelines        | 41 |

|   |      | 3.1.2 Instance-level guidelines           | 43 |

|   |      | 3.1.3 Action language assumptions         | 44 |

|   |      | 3.1.4 Simplification assumptions          | 44 |

|   | 3.2  | Examples                                  | 46 |

|   |      | 3.2.1 Dwarf Signal                        | 46 |

|   |      | 3.2.2 The Leadership Election Problem     | 49 |

|   |      | 3.2.2.1 The Abstract SysML model          | 49 |

|   |      | 3.2.2.2 The Concrete SysML model          | 50 |

|   | 3.3  | Semantic rules metalanguage               | 52 |

|   | 3.4  | Overview of the semantics of SysML models | 54 |

|   | 3.5  | Final remarks                             | 59 |

| 4 | Stru | ictural Diagrams                          | 60 |

|   | 4.1  | Overview                                  | 60 |

|   | 4.2  | Operations and signals                    | 63 |

|   | 4.3  | Interfaces                                | 65 |

|   | 4.4  | Standard ports                            | 66 |

|   | 4.5  | Simple blocks                             | 70 |

|   |      | 4.5.1 Simple blocks: types                | 71 |

|   |      | 4.5.2     | Simple b          | locks: cl | hannels   |         |       |            |       | <br> |      |      | <br> |  | 72  |

|---|------|-----------|-------------------|-----------|-----------|---------|-------|------------|-------|------|------|------|------|--|-----|

|   |      | 4.5.3     | Simple b          | locks: pi | rocesses  | S       |       |            |       | <br> |      |      |      |  | 73  |

|   |      | 4.5.4     | Simple b          | locks: co | ontrolle  | r proce | ess   |            |       | <br> |      |      |      |  | 85  |

|   | 4.6  | Compo     | site block        | s         |           |         |       |            |       | <br> |      |      |      |  | 89  |

|   | 4.7  | Related   | d Work .          |           |           |         |       |            | <br>• | <br> |      |      |      |  | 96  |

| 5 | Beha | avioural  | Diagram           | ıs        |           |         |       |            |       |      |      |      |      |  | 98  |

|   | 5.1  | State M   | Iachine D         | iagram .  |           |         |       |            |       | <br> | <br> |      | <br> |  | 98  |

|   | 5.2  | Activit   | y Diagram         | 1         |           |         |       |            |       | <br> | <br> |      | <br> |  | 101 |

|   |      | 5.2.1     | Overview          | v         |           |         |       |            |       | <br> |      |      | <br> |  | 101 |

|   |      | 5.2.2     | Example           | s         |           |         |       |            |       | <br> |      |      | <br> |  | 103 |

|   |      | 5.2.3     | Formal se         | emantics  | s         |         |       |            |       | <br> |      |      | <br> |  | 105 |

|   |      |           | 5.2.3.1           | Block     | Activity  | Diagr   | ams   |            |       | <br> |      |      | <br> |  | 105 |

|   |      |           | 5.2.3.2           | Single    | Activity  | / Diagi | ram   |            |       | <br> | <br> |      | <br> |  | 110 |

|   |      |           | 5.2.3.3           | Interna   | ıl Activi | ty Dia  | gran  | ı.         |       | <br> |      |      | <br> |  | 110 |

|   |      |           | 5.2.3.4           | Main A    | Action .  |         |       |            |       | <br> |      |      | <br> |  | 114 |

|   | 5.3  | Related   | d work .          |           |           |         |       |            |       | <br> |      |      |      |  | 116 |

| 6 | Sequ | ience Di  | iagram            |           |           |         |       |            |       |      |      |      |      |  | 119 |

|   | 6.1  | Overvi    | ew                |           |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 119 |

|   | 6.2  | Formal    | semantics         | s         |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 121 |

|   |      | 6.2.1     | Lifeline          |           |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 123 |

|   |      | 6.2.2     | Messages          | s         |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 125 |

|   |      | 6.2.3     | Combine           | d fragm   | ents      |         |       |            |       | <br> | <br> | <br> | <br> |  | 129 |

|   |      | 6.2.4     | State inva        | ariant    |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 131 |

|   |      | 6.2.5     | Main act          | ion       |           |         |       |            |       | <br> | <br> |      | <br> |  | 132 |

|   | 6.3  | Related   | d work .          |           |           |         |       |            |       |      |      |      |      |  |     |

| 7 | Mod  | lel Integ | ration            |           |           |         |       |            |       |      |      |      |      |  | 136 |

|   | 7.1  | Non-hi    | erarchical        | models    |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 137 |

|   | 7.2  | Hierard   | chical mod        | lels      |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 141 |

|   | 7.3  | Scenar    | ios               |           |           |         |       |            |       | <br> | <br> | <br> | <br> |  | 143 |

|   | 7.4  | Related   | d Work .          |           |           |         |       |            | <br>• | <br> |      |      |      |  | 144 |

| 8 | Mod  | lel Anal  | ysis and <b>V</b> | Validatic | on of the | e sema  | ıntic | e <b>s</b> |       |      |      |      |      |  | 148 |

|   | 8.1  | Mecha     | nisation of       | f the Tra | nslation  | Proce   | SS    |            |       | <br> | <br> | <br> | <br> |  | 149 |

|   | 8.2  |           | tency Che         |           |           |         |       |            |       |      |      |      |      |  | 152 |

|   | 8.3  |           | ing SysMl         | •         |           |         |       | -          | •     |      |      |      |      |  |     |

|   |      | 8.3.1     | Analysis          |           |           |         |       |            |       |      |      |      |      |  |     |

|   | 8.4  | Validat   | ion of the        |           | -         |         |       |            |       |      |      |      |      |  |     |

|    |        | 8.4.1          | Inserting a private operation     | 166 |

|----|--------|----------------|-----------------------------------|-----|

|    |        | 8.4.2          | Inserting a private attribute     | 16  |

|    |        | 8.4.3          | Decomposition of a block          | 16  |

|    | 8.5    | Related        | d Work                            | 17  |

|    | 8.6    | Final R        | Remarks                           | 172 |

| 9  | Con    | clusion        |                                   | 174 |

|    | 9.1    | Future         | Research                          | 17  |

| Re | eferen | ces            |                                   | 179 |

| Ar | pend   | ix             |                                   | 180 |

| -  | -      |                |                                   |     |

| A  |        | nslation       |                                   | 187 |

|    | A.1    |                | for Activity                      |     |

|    |        | A.1.1          | Call Behaviour Action Parallelism |     |

|    |        | A.1.2          | Start Activity                    |     |

|    |        | A.1.3<br>A.1.4 | Interruptible Regions             |     |

|    |        | A.1.4<br>A.1.5 | Interrupt Activity Manager        |     |

|    |        | A.1.5<br>A.1.6 | Token Manager                     |     |

|    |        | A.1.7          | Action Types                      |     |

|    |        | A.1.8          | Action Incoming Edges             |     |

|    |        | A.1.9          | Action Outgoing Edges             |     |

|    |        |                | Call Operation action             |     |

|    |        |                | Opaque action                     |     |

|    |        |                | Send Signal action                |     |

|    |        |                | Value Specification action        |     |

|    |        |                | Accept Event action               |     |

|    |        |                | Call Behaviour action             |     |

|    |        |                | Read Self action                  |     |

|    |        |                | Read Structural Feature action    |     |

|    |        | A.1.18         | Control Nodes                     | 21  |

|    |        | A.1.19         | Initial Node                      | 212 |

|    |        | A.1.20         | Flow Final Node                   | 213 |

|    |        | A.1.21         | Activity Final Node               | 214 |

|    |        |                | Decision Node                     |     |

|    |        | A.1.23         | Merge Node                        | 216 |

|    |        |                | Fork Node                         |     |

|    |        | A.1.25         | Join Node                         | 21  |

|      | A.1.26 Object Nodes                         |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                           |

|------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|      | A.1.27 Input Pin                            |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                           |

|      | A.1.28 Activity Parameter                   |                                                                                                                                                                                                                                                                                                                                                                                                                                    | .0                          |

|      | A.1.29 Output Pin                           |                                                                                                                                                                                                                                                                                                                                                                                                                                    | .2                          |

|      | A.1.30 Data Store                           |                                                                                                                                                                                                                                                                                                                                                                                                                                    | .3                          |

|      | A.1.31 Channel sets                         |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                           |

| A.2  | Rules for Sequence diagram                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                           |

|      | A.2.1 Combined fragments                    |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                           |

|      | A.2.1.1 PAR                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                           |

|      | A.2.1.2 STRICT                              |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                           |

|      | A.2.1.3 OPT                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                           |

|      | A.2.1.4 BREAK                               |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                           |

|      | A.2.1.5 CRITICAL                            |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                           |

|      | A.2.1.6 LOOP                                |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                           |

|      | A.2.2 InteractionUse                        |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                           |

| Pre- | e-processing of the CML models              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                           |

| B.1  | Procedures                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                           |

|      | B.1.1 Procedures for Animation              |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                           |

|      | B.1.2 Procedures for Model Checking         |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                           |

| Sema | nantic Validation Models                    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                           |

| C.1  | CSP model of the refinement for inserting a | private operation 25                                                                                                                                                                                                                                                                                                                                                                                                               | 3                           |

|      |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |

| C.2  | CSP model of the refinement for inserting a | private attribute 25                                                                                                                                                                                                                                                                                                                                                                                                               | 8                           |

|      | Pro<br>B.1                                  | A.1.27 Input Pin  A.1.28 Activity Parameter  A.1.29 Output Pin  A.1.30 Data Store  A.1.31 Channel sets  A.2 Rules for Sequence diagram  A.2.1 Combined fragments  A.2.1.1 PAR  A.2.1.2 STRICT  A.2.1.3 OPT  A.2.1.4 BREAK  A.2.1.5 CRITICAL  A.2.1.6 LOOP  A.2.1 InteractionUse  Pre-processing of the CML models  B.1 Procedures  B.1.1 Procedures for Animation  B.1.2 Procedures for Model Checking  Semantic Validation Models | A.2.1 Combined fragments 23 |

## 1

### Introduction

One of the most critical aspects in system development consists in the difficulty to assess specification compliant products. Among the factors that influence this issue we can cite the increasing complexity of engineered systems, the effectiveness of the applied methods and budget constraints (DEBBABI et al., 2010). The increasing size and complexity of systems have led to a great difficulty to their description and specification. Features like concurrency and parallelism demand notations and techniques for reasoning about system properties. In a broader context, Systems Engineering is related to the design of whole systems through an iterative process that leads to the development and operation of a system. Overall, system engineering is an interdisciplinary approach to the development of systems (BOARD, 2006). In this case, systems are not only software-intensive but can also involve physical components.

In particular, verification and validation (V&V) tasks must evolve accordingly in order to tackle the increasing size and complexity of systems. The current methodologies based mainly on testing are not effective enough to critical systems due to the impossibility of assuring correctness. In addition, the detection of failures in the early stages of development produces several benefits and a higher return on investment because the maintenance time, effort and costs are decreased. According to Boehm (BOEHM, 1981), fixing a defect after delivery can be considerably more expensive than fixing it during the requirements and the design phases. Hence, in order to reduce risks and costs in systems engineering, activities related to V&V should be performed as early as possible, thus, increasing the quality and reliability of systems.

In some categories of systems, like critical real-time systems where safety is a major concern, early V&V is essential to support their expensive and long-term development process. These activities play a crucial role because of the danger of losing human lives due to system failures. In this context, besides testing, other approaches using formal techniques should be applied to increase the level of reliability on such systems. However, few verification approaches are supported by formal foundations.

Some desired characteristics in the V&V approach are listed below:

Provide automated mechanisms. Automation optimises the V&V process and avoids the introduction of errors by human-related activities.

- Use formal and rigorous reasoning to reduce errors due to ambiguity.

- Use a graphical modelling language to ease the understanding of the system, hiding an underlying formal model.

Regarding the verification of systems and software, two formal approaches have been proposed to tackle this challenge, theorem proving (GOUBAULT-LARRECQ; MACKIE, 1997) and model checking (CLARKE et al., 1999). Theorem proving deals with first-order or higher-order logic, which allows the verification of infinite state systems. On the other hand, model checking works with decidable logics and is limited to deal with finite state systems. Hence, the effectiveness of model checking is reduced when the system exhibits an enormous (or infinite) number of states. This limitation is well know as the *exponential state explosion problem* (CLARKE et al., 2012). Applying model checking to a system with these characteristics may consume all memory resource of a computer and return no response at all.

Nevertheless, even with this limitation, model checking has proven to be a successful approach for verifying the behaviour of software and hardware applications (MILLER et al., 2010). The reason for this resides in the fact that this technique is fully automated. Model checkers traverse all possible states of a system specification in order to evaluate properties in an automated manner. If a property is not satisfied, a counterexample is returned, which indicates a possible flaw in the system. Such flaw can be corrected and the property analysed again, allowing an iterative process to validate systems.

According to Clarke (CLARKE et al., 1999), model checking means the automatic verification of satisfiability of the relation  $M \models p$ . In other words, does the model M, which is described as a transition system, satisfy the property p, which is described as a logical formula? Roscoe (ROSCOE, 1997, 1998) proposes a variation of this statement where the refinement  $S_p \sqsubseteq S_m$ , given that  $S_p$  and  $S_m$  are CSP (HOARE, 1985) specifications and  $S_p$  is known to exhibit the property p, provides an equivalent response to  $M \models p$ . However, as both specifications are CSP processes, what we are checking in fact is if the process  $S_p$ , which is defined in a lower level of abstraction than  $S_m$ , has all the behaviours of  $S_m$ . This approach is called *refinement model checking*. The model checker FDR (Failures-Divergences Refinement) (GIBSON-ROBINSON et al., 2014) and PAT (SUN et al., 2008), for instance, allow the verification of such refinements by transforming a CSP specification into labelled transition system (LTS) with the purpose of refinement checking.

Although this approach has been applied in industry, there is an issue regarding the notations used by these tools. Usually they require specifications to be written using formal notation, which is usually based on a text format and is difficult to understand for users not familiar with formal languages. Therefore, making system engineers adopt a formal notation in their daily tasks becomes a challenge. System practitioners usually work with graphical notations because they are easy to understand and communicate to other stakeholders. Among this category of languages, UML (Unified Modelling Language) (OMG, 2011) has become an

established standard in both academia and industry for modelling software.

Following the success of UML, a profile for systems engineering, called SysML, has been defined (OMG, 2010a) and has become a *de facto* standard in the area. There is wide availability of basic literature (HOLT; PERRY, 2008; FRIEDENTHAL et al., 2011), and tools from vendors like IBM (IBM, 2013), Atego (ATEGO, 2013), and Sparx Systems (SYSTEM, 2013) for SysML.

Like UML, SysML has an informal semantics, with several points left loose. Flexibility of usage for capturing requirements, and for model development and evolution, is prioritised over a well-defined semantics. In systems engineering, however, there are areas of application for which rigour is essential, and the danger of misunderstanding models due to different interpretations of their meaning is not acceptable. Moreover, the use of models in automated techniques for analysis and verification requires the definition of a semantics of the diagrammatic notation in terms of desired formal syntax.

In the past years a considerable effort has been spent to fill this gap between graphical modelling languages and formal languages. This can be achieved by transformations between models, where a source model defined using a graphical language can be transformed into a target model related to a formal specification. The advantage of this approach is to reuse the tool support of the formal notation. Usually, the approaches differ in the modelling language chosen, the formal domain to represent its semantics, the amount of constructs that can be translated and the level of automation provided.

The COMPASS project <sup>1</sup> was the pioneer in proposing model-based methods and tools for the development and analysis of System of Systems (SoS), which is a category of systems where independent constituent systems cooperate in order to achieve a common goal (JAMSHIDI; JAMSHIDI, 2009). It was composed by research groups of five universities (Newcastle University, Aarhus University, University of York, Bremen University and Universidade Federal de Pernambuco) and three companies (Atego, Bang & Olufsen and Insiel) and was funded by the seventh framework programme (FP7) of the European Union. These groups collaborated to advance the state of the art for the development and maintenance of SoS. Among its achievements we can cite the COMPASS Modelling Language (CML), which is a formal language based on a state-rich process algebra, a tool environment for creating and analysing CML specifications, tools for deriving CML specifications from SysML models, and a process for analysing SysML models. Our research was part of the COMPASS project. We have worked in the definition of the formal semantics of SysML diagrams to allow its automatic derivation from SysML tools and we have proposed approaches for analysing SysML models.

Our work enables the use of refinement-based analysis and verification to reason about SysML models. Many have pursued formalisation of both SysML and UML: there are formalisations of individual diagrams, a few examples of which are (GRAVES; BIJAN, 2011a; RAMOS et al., 2005; STORRLE, 2004a; ABDELHALIM et al., 2010), and of models that combine

<sup>&</sup>lt;sup>1</sup>http://www.compass-research.eu/

diagrams (DAVIES; CRICHTON, 2003). Typically, the approaches that tackle collections of diagrams deal with very constrained subsets of the notation of the individual diagrams. We focus on diagrams that facilitate design, namely the block definition, internal block, state machine, activity, and sequence diagrams. Our work is distinctive both in its coverage of the available notation to write each of these diagrams, and in its integrated approach, where the semantics of all diagrams are integrated into a single formal model. We have chosen not to extend previous work for several motives: the lack of integration between the SysML model elements we chose, the semantic domain were considerable distinct from CML, and, even the works that have a close relationship with CML, like the ones for CSP, do not define their semantics following a compositional approach like we do.

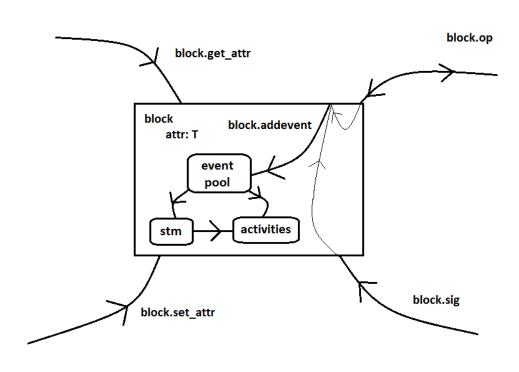

We define a single formal model that captures data and behavioural aspects of a SysML model that gives an overall picture of a system using a collection of diagrams. Our semantic domain (formal modelling language) is CML (WOODCOCK et al., 2012a), a state-rich process algebra for refinement. We define a semantics for SysML models via mapping into CML.

Our goal is to support reasoning at the level of the diagrammatic notation by using an underlying model described in CML together with formal method techniques and tooling. Accordingly, we describe here a semantics that can be used for automatic generation of CML models from diagrams. It takes the form of a function that maps SysML to CML and is defined by transformation rules. It is implemented in a model-generation tool based on Atego's Artisan Studio SysML tool (ATEGO, 2013).

To enable the construction of meaningful CML models, we define usage guidelines for SysML. They are important to guarantee a minimal level of concreteness of the SysML model in order to be able to reason about it. Basically, block diagrams are used to define the system and its components, internal block diagrams to define the relationship between them, each operation is defined in a state machine or in an activity diagram, but not both, and sequence diagrams define scenarios of the system. Our guidelines ensure that we can produce useful CML models that are very comprehensive and impose few restrictions to the user. We illustrate these guidelines and the use of refinement using two industrial case studies: the leadership election protocol, which is used in an industrial multimedia system of systems, and the dwarf signal, which is a hardware device used to control traffic of trains in railways.

The CML semantics for block, internal block, activity, and sequence diagrams have been presented in (MIYAZAWA et al., 2013; LIMA et al., 2013, 2014) and they are direct results of our work. Another contribution is a revised and integrated version of these semantics (LIMA et al., 2015) including the semantics of state machine diagrams, which was defined by Miyazawa (MIYAZAWA et al., 2013) and is not a contribution of this thesis but is nevertheless explained here as it is part of the integrated modelling approach proposed. The definition of these semantics in CML enables their use to analyse properties of the individual diagrams, like refinement of models, for instance, assuring that the actual version of a state machine is a refinement of an earlier version, and absence of deadlock, livelock and non-determinism in

these models. In addition, we propose an analysis methodology considering the integrated model where traces and general properties of the system can be verified.

Using our CML semantics, we can use refinement to analyse properties of diagrammatic models. We propose an approach where a system model can be built using block definition and internal block diagrams to represent the structural part of the system, and state machines and activity diagrams to model the behavioural aspects. Valid scenarios, including desired properties of the system can be modelled using sequence diagrams, which we call the validation model. Finally, we can check if the system model behaves according to the validation model using refinement checking.

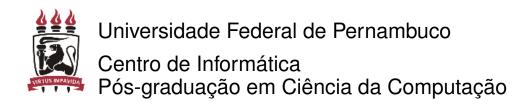

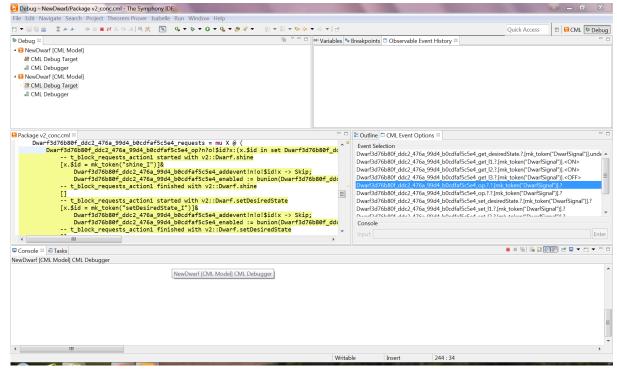

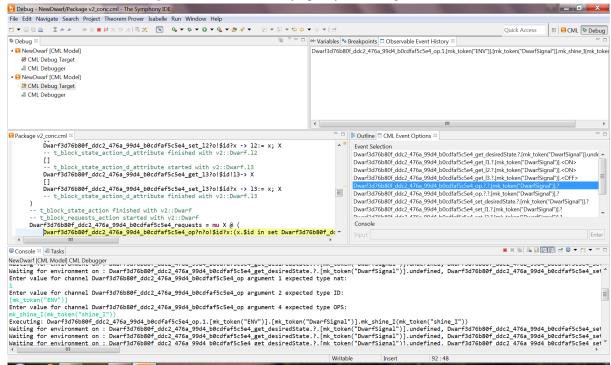

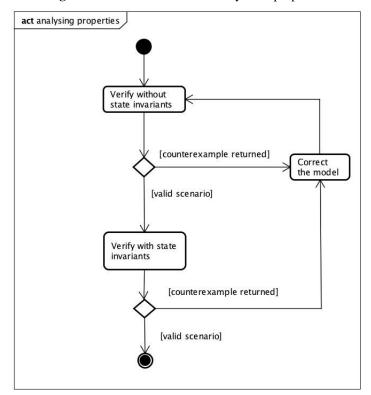

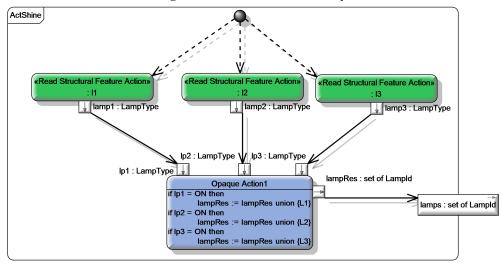

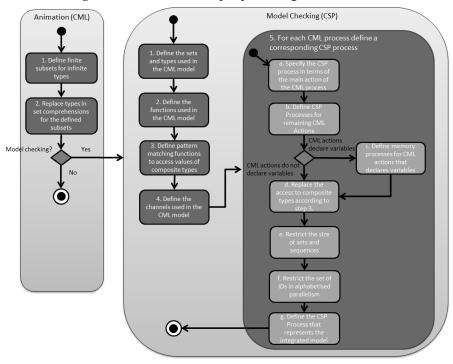

Figure 1.1 illustrates the process of the verification activities of our approach. In step one, system engineers build SysML models using the Artisan Studio tool. Step 2 corresponds to the automatic transformation of the SysML models into CML models. The generated CML models follow the definitions of our semantics. The translation was implemented by Atego and is not part of this work. The resultant CML models can be either animated or analysed through refinement checking. Step 3 shows the transformations of the CML model into a concrete version able to be animated. This step uses a tool implemented in the scope of this thesis. This tool outputs a new version of the CML model that can be used in the Symphony tool (COLEMAN et al., 2012) for animation in Step 4. For refinement checking analysis, we need to transform our CML models into CSP specifications in Step 5, which are analysed using the FDR model checker in step 6. Despite being a overhead transforming CML to CSP, this is minimised due to the fact that CSP is one of the baseline languages of CML, and they have similar underlying semantics both based on the Unifying Theories of Programming (HOARE; HE, 1998).

In summary, our main contributions are:

- Guidelines of usage for construction of meaningful SysML models (by meaningful, we mean models that can be translated to a formal model in CML);

- State-rich process algebraic semantics for the following SysML diagrams:

- sequence diagram;

- activity diagram;

- block definition diagram;

- internal block diagram;

- An integrated semantics that combines activity, block definition, internal block, state machine and sequence diagrams;

- An analysis approach for verifying scenarios and properties of SysML models;

- Mechanisation of the process used to transform CML models to allow their animation in the Symphony tool;

**Figure 1.1:** The process of our approach.

Source: Author's ownership.

- Guidelines for translating CML models into CSP;

- Development of two industrial case studies.

### 1.1 Structure of the Thesis

Chapter 2 describes the two baseline languages used in the proposed approach. First, the graphical modelling language SysML is described in terms of its diagrams and its relationships with its parental language UML. We also discuss the informal semantics of some constructs presented along the document. It is important to understand the SysML language because models of this language are the inputs to our strategy. Next, we describe the COMPASS Modelling Language (CML), the semantic domain used to define SysML models formally. CML is a formal language that allows the specification of models using state-rich elements and a process algebra. As the SysML constructs are mapped to CML specifications, it is important to understand the syntax and semantics of the constructs used in the CML language as well.

Chapter 3 presents how SysML models must be constructed in order to provide meaningful models, which can be represented in CML according to our semantics. The following chapters detail the isolated semantics of each one of the diagrams of SysML addressed in the thesis.

Chapter 4 presents the CML semantics provided for block diagrams (block definition and internal block diagrams), which covers the structural part of SysML models. Chapter 5 describes the CML semantics for SysML state machine and activity diagrams, both covering the

behavioural part of SysML models. Chapter 6 presents the CML semantics for SysML sequence diagrams, which are used to build scenarios of the system that are used to validate the model (as described further in Chapter 8). Although the state machines semantics is not a contribution of this thesis, it is important to understand its semantics when we discuss in Chapter 7 the integrated semantics of all diagrams. We present the related work in each chapter in order to make a clearer relation with our contributions.

Chapter 8 presents some applications of our integrated semantics regarding analysis of SysML models. It describes the mechanisation of the CML models generation from SysML models using the Atego's Artisan Studio tool. Then, it describes how models can be animated, which can be used to understand the communication between the entities of the SysML model, and, as another contribution of this thesis, a strategy to analyse systems modelled in SysML based on scenarios specified in sequence diagrams. This strategy uses the refinement capability of the generated models to verify if the traces of the sequence diagrams are valid in the traces of the model resulted from the combination of the other diagrams. This chapter also provides some validations of our semantics through the exercise of refinements at the SysML level.

Finally, in Chapter 9, we consider what are the benefits of using an integrated semantics for SysML diagrams and the practical advantages and limitations of using our semantics in formal-based tools. We also present what still needs to be done as future research.

# 2

### **Background**

In this chapter we describe the modelling languages used in the context of this work. Section 2.1 describes SysML, which is the diagrammatic language used as baseline of our approach, while Section 2.2 describes the semantic domain used as the formal semantics of SysML, which is described in terms of the state-rich and process algebraic language, CML.

### 2.1 SysML

SysML, which is a standard of the Object Management Group (OMG, 2012), is a modelling notation for systems engineering, defined as a UML 2.0 profile. SysML allows the representation of systems, hardware, software, information and processes, with the objective of providing dedicated support for system-level modelling, verification and validation. Like UML, SysML provides a number of diagrams to support the description of different aspects of a system. SysML has the following prominent distinctive features that are not present in UML:

- The "classical" software-centric focus present in UML, through class diagrams and composite structure diagrams, has been moved to the system-level in SysML by the introduction of block definition diagrams and internal block diagrams (OMG, 2012, Chapter 8).

- The general UML notion of constraints has been strengthened in SysML through the introduction of constraint blocks and parametric diagrams (OMG, 2012, Chapter 10).

- A notation for requirements engineering and tracing from model elements to requirements (OMG, 2012, Chapter 16).

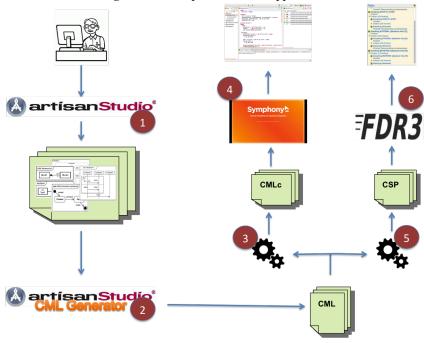

The Venn diagram shown in Figure 2.1 displays how the two languages, UML2 and SysML, relate to each other. The intersection between the two circles represents the constructs from UML reused by SysML, which is called the UML4SysML subset. The part of the SysML circle that is not part of the UML 2 circle indicates the new modelling constructs of SysML that are not present in UML, or that replace UML constructs. There is a part of UML that is not required in SysML, which is marked "UML not required by SysML".

**Figure 2.1:** Overview of the relationship between UML 2 and SysML.

Source: (OMG, 2012)

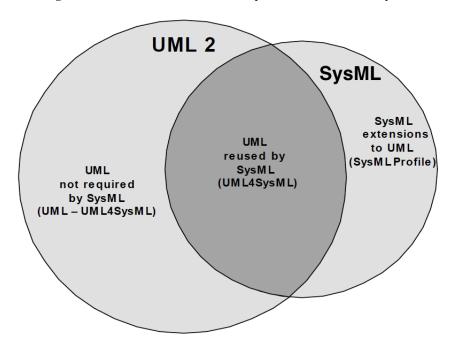

Figure 2.2 shows a representation of the organisation of the SysML diagrams. Basically, SysML provides nine types of diagrams to model systems. Some of them are completely reused from UML, like sequence diagram, state machine diagram, use case diagram and package diagram. Some others were modified to be consistent with SysML extensions. Block definition diagram and internal block diagram are similar to UML class diagram and composite structure diagram, respectively. UML activity diagram has also been extended. There are two new types of diagrams, requirements diagram and parametric diagram. A requirement diagram provides constructs for text-based requirements, and the relationship between requirements and other model elements that satisfy or verify them. Parametric diagram describes constraints among the properties associated with blocks. Its purpose is to integrate behaviour and structure models with engineering analysis models such as performance and reliability.

The details on the informal syntax and semantics of the diagrams and their constructs is available in (OMG, 2012). Additionally, other sources of literature (HOLT; PERRY, 2008; FRIEDENTHAL et al., 2011) describe the language with the support of real word examples focusing on architectural modelling.

This thesis does not provide semantics for all SysML diagrams. We cover block definition diagram, internal block diagram, activity diagram and sequence diagram. State machine diagram is discussed here as part of the integrated approach but its semantics has been provided separately by partners of the COMPASS project (MIYAZAWA et al., 2013). However, the chosen subset provides means to describe both structure and behaviour of a system. Despite having nine types of diagrams, SysML does not require all diagrams to be used during modelling tasks. It depends

**Figure 2.2:** SysML diagram taxonomy.

Source: (OMG, 2012).

on what needs to be represented. System designers may only be interested in modelling the behavioural part of a system, or just the structural part, or both, and for that they may choose the diagrams to be used according to their expertise or tools that are available for use.

In this section, we shall briefly describe the parts of SysML structural and behavioural diagrams that are relevant in the context of our semantics of SysML in terms of CML.

### 2.1.1 Block-definition diagram

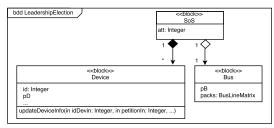

A block-definition diagram depicts blocks and their relationships. A block can represent any abstract or real entity: a piece of hardware, a software, or a physical object, for instance. The whole system is also represented by a block. Figure 2.3 shows a diagram of our case study: a distributed system of systems (devices) that automatically elects a leader among them. A possible scenario of this case study is a house with a television, a cell phone and a home stereo that must provide a synchronised experience to the costumer. However, to achieve that they must elect a leader between the three devices that manage the data that allows the synchronism between them. In this diagram, there are three blocks: SoS represents the complete system (of systems), Device, three devices, and Bus, one bus.

Blocks can have attributes and operations. Attributes are properties of a block. For instance, in Figure 2.3, id is an integer attribute of the block Device, and packs is an attribute of Bus. The attributes pD and pB are ports, which are used for connecting blocks and are further discussed in the next section.

An operation captures functional behaviour provided by the block. For instance, Device is able to update its state via the operation updateDeviceInfo(). Operations are typically triggered by synchronous requests. A signal, on the other hand, does not have a specific behaviour, but may

**Figure 2.3:** A block definition diagram.

Source: Author's ownership.

Figure 2.4: An example of an internal block diagram.

Source: Author's ownership.

trigger behaviours in state machines and activities. It is used for asynchronous communication between blocks (or with the environment).

A block can be related to another by an association, which can be over different multiplicities and indicates a potential relationship between instances of the blocks. Blocks can also be related by composition, indicated by an arrow with a filled diamond at one end. A composition establishes a whole-part relationship: the block at the diamond end is the whole composite block and those at the other end are the parts. The main feature of a composition is that a part, that is, an instance owned by the composition, may belong to at most one block. In our example, SoS is a composite block; its parts are three instances of a Device and one instance of a Bus.

### 2.1.2 Internal block diagram

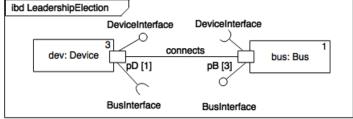

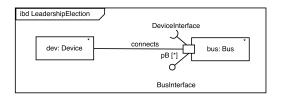

Internal block diagrams are similar to block definition diagrams, but typically show the internal connections between parts of a block. Figure 2.4 shows the parts of the leadership election protocol.

In this example, three instances of a Device are connected to one instance of a Bus. This is defined via the connector between the ports pD and pB, represented by a solid line. In fact, each connection between each port should be explicit represented in the model, however, we have grouped all connections in one solid line for simplification. A connector links two or more instances of a block either directly or via ports, like in the example, to allow them to communicate. This is in contrast with an association, which specifies that there can be links

**Figure 2.5:** A state machine diagram.

Source: Author's ownership.

between any instances of the associated blocks, rather than that there is a link between particular instances.

If there is an association between the blocks that define the instances directly linked by a connector, we say that this connector realises the association, and that the association defines the type of the connector. Connectors that do not realise an association are not typed.

The ports pD and pB define provided and required interfaces. A provided interface is depicted as a circle and identifies a port that produces outputs to its client. A required interface is depicted as a semicircle and identifies a port that takes inputs from its client.

The number in a port defines its arity. For instance, each device has a port pD with arity one, whereas the port pB of the single instance of the bus has arity 3. This allows the connection of one bus with three devices.

### 2.1.3 State-machine diagram

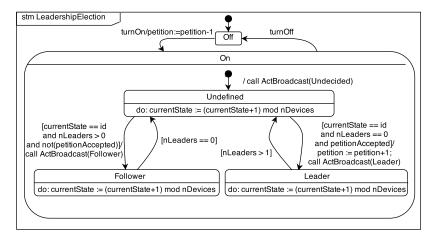

The state-machine diagrams of both UML and SysML are compatible (OMG, 2010b, pp. 541). A state-machine diagram reacts to events from the environment, which are stored in an event pool. The order in which events in the pool are processed is unspecified. Figure 2.5 shows an example of a state machine from our case study.

States can be simple or composite. Simple states do not have substates. For instance, Off in Figure 2.5 is a simple state, while On is a composite state. Initial states are depicted as filled circles. Figure 2.5 shows two initial states: the initial state of the entire state-machine diagram and the initial state of the state On.

A state may have three types of behaviour: entry and exit actions, and do activities. Entry actions are executed when the state is activated, exit actions are executed when the state is exited, and do activities are executed when the state finishes activating. Do activities may either stop by themselves or continue indefinitely until a transition interrupts it and exits the

state. Figure 2.5 shows the do activities performed by the states Undefined, Follower and Leader. These activities store in the currentState the value of the new state: currentState+1 modulo the number (nDevices) of devices.

A transition connects a source to a target state; it may contain a trigger, a guard and a behaviour. The trigger and guard are separated from the behaviour by a slash (/). Guards are specified between square brackets. For example, in Figure 2.5, the transition from the state Off to the state On is triggered by a signal turnOn and it has no guard. On the other hand, the transition from Undefined to Leader takes place whenever the state Undefined is active, its do activity has finished, and the guard currentState == id and nLeaders == 0 and petitionAccepted is true (this means that a device becomes a leader whenever its petition has been accepted and there are no leaders). The system returns to Undefined whenever more than one leader is elected. Similarly, the transition from Undefined to Follower takes place whenever Undefined is active, its do activity has terminated, and the guard currentState == id and nLeaders > 0 and not(petitionAccepted) evaluates to true. This means that the device becomes a follower whenever there is at least one leader and it is not itself (because its petition was not accepted). The transition from Follower to Undefined happens whenever the source state is active, the do activity has terminated and nLeaders == 0 holds, i.e. it happens whenever there are no leaders. In our semantics, we restrict behaviours to be any CML action language statement, like the assignment petition := petition + 1 displayed in Figure 2.5. Also, operation calls, signals and call to activities can be used as descriptions of behaviour by using the CML action language. The latter is illustrated in Figure 2.5 where the activity ActBroadcast is invoked in the behaviours of some transitions. The syntax of the CML action language is detailed in Chapter 3.

For the purpose of this work we divide transitions between completion and non-completion transitions. Completion transitions are triggerless transitions that are executed when the internal behaviour of the state (e.g, "do activities") terminates. Non-completion transitions are triggered by events from the event pool and can interrupt the internal events of its source states. For instance, the transition from Off to On is a non-completion transition because it is triggered by the event turnOn, while the transition from Follower to Undefined is a completion transition because it has no trigger, it only requires the do activity from Follower to terminate and the guard between the states to be true.

A transition between two states, whose trigger and guard (if any) are evaluated to true, can be executed by exiting the source state, executing the transition behaviour and entering the target state. In the general case, transitions can cross state boundaries; this requires that not only the source state is exited by the transition, but some of its ancestors too.

Finally, state machines may contain join, forks, junction and choice states. These states are used to control the flow through the states. Join and fork states (both represented by solid bars) gather and split transitions, respectively. A junction state (represented graphically by a solid black circle) provides a mechanism for choosing which transition (leaving the junction state) to follow. Transitions leaving junction states cannot have triggers, and the evaluation of the

**Figure 2.6:** Example of an activity diagram.

Source: Author's ownership.

guard is performed prior to the execution of the transition. An alternative is the choice state that provides a mechanism for choosing the particular transitions to follow, but, unlike junction states, the decision of which transition to follow is performed during the execution of the transition path. Therefore, the execution of the behaviours of the transitions in the path can affect the outcome of the execution of the choice state.

### 2.1.4 Activity diagram

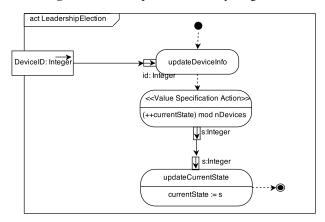

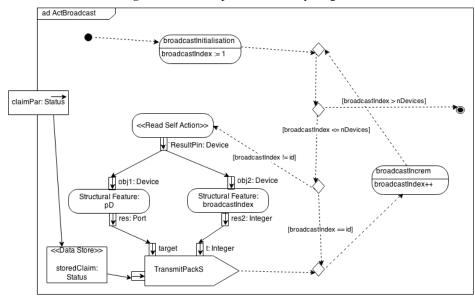

Activity diagrams are based on classic flow charts. In contrast with the other diagrams, they are normally used for low-level modelling: detail the behaviour of an operation and describe workflows or processes.

An activity diagram has three basic elements: activity nodes, edges and regions. An activity node represents an action, a control or an object. An action node is used to represent some action. In Figure 2.6, the nodes with names updateDeviceInfo, <<Value Specification Action>> and updateCurrentState are action nodes. The node named <<Value Specification Action>> computes the value of an expression (++currentState) mod nDevices that is then sent to updateCurrentState via the output pin s.

Control nodes manipulate the flow of actions, for example, via decisions, forks and joins. Figure 2.7 illustrates the possible control nodes. A decision node chooses among its outgoing edges according to their guards or probabilities. Only one outgoing edge must be chosen. If more than one guard is true, the order of evaluation is not defined. A merge node brings together multiple flows without synchronisation. A fork node splits a flow into multiple concurrent flows. A join node synchronises multiple flows. An initial node starts the flow when the activity is invoked. An activity may have more than one initial node, then invoking an activity starts multiple flows. A flow final node destroys all tokens that arrive at it. It has no effect on other flows in the activity. An activity final node terminates the activity. An activity may have more than one activity final node. The first activity final node reached stops all flows in the activity.

Figure 2.7: Control nodes.

Activity final

- Final nodes -

Flow final

Source: (OMG, 2011).

Fork node, join node

Decision node

or Merge node

Object nodes represent data used by an activity: inputs and outputs to the activity or to its nodes. Among the object nodes, the most used ones are parameters pins and datastores. For example, in Figure 2.6, DeviceID is a parameter object node of the activity and its data is taken as input by the node updateDeviceInfo via the pin id, which is also an object node. A datastore is an object node that can repeatedly provide in its outgoing edges the data received until the activity terminates or another data arrives in the node.

Edges can be of two types: control flow or object flow. A control flow defines when and in which order the actions run. Control flows are shown as dashed arrows. An object flow describes how inputs and outputs flow between actions. Object flows are depicted as solid arrows; in Figure 2.6 the Deviceld object is passed to the action updateDeviceInfo and ((++currentState) mod nDevices) is sent to updateCurrentState.

Activity diagrams use a token semantics to control the flow of execution. A node can be executed only when all its inputs have received tokens, and, once it finishes its behaviour, it provides tokens on its outputs. Some nodes create tokens (for instance, an initial node only provides tokens on its outputs), while others remove tokens (for instance, a flow final node only consumes tokens that arrive on it). An activity diagram finishes its execution when there is no token flowing through it or an activity final node is reached.

### 2.1.5 Sequence diagram

In UML 2.0, there are four types of diagrams to describe interactions: sequence diagrams, communication diagrams, interaction overview diagrams, and timing diagrams. Among them, the sequence diagram is the most commonly used to describe interaction aspects of systems, and therefore SysML considers only sequence diagrams to describe interactions. According to the SysML specification (OMG, 2012), communication diagram and interaction overview diagrams are excluded as they overlap in functionality without adding significant capabilities for modelling systems. Timing diagrams are not included because of their lack of maturity and suitability for systems engineering needs.

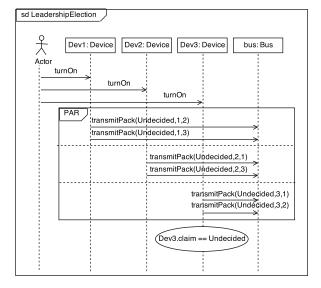

A sequence diagram describes operational scenarios of a system with an emphasis on order. This is achieved through the use of lifelines. Each participant of the diagram, typically, instances of blocks or its parts, possesses a lifeline, so that we can represent a message-exchange order.

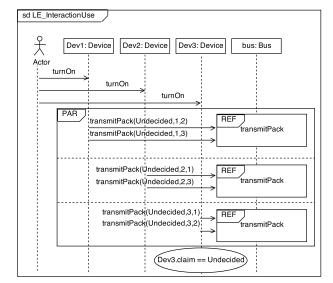

The sequence diagram in Figure 2.8 presents a scenario of the leadership election example

**Figure 2.8:** Example of a sequence diagram.

Source: Author's ownership.

where a user turns on three devices and each of them notifies the bus that the leader is undefined. The user is depicted as an actor, while the three Devices Dev1, Dev2, Dev3 are instances of block Device and bus is an instance of block Bus. A lifeline is represented by a dashed vertical line under each participant.

Participants communicate via messages. For example, Figure 2.8 shows the actor sending messages to turn on devices. Messages are sent in sequence along a participant lifeline. So, the first message sent by the actor goes to Dev1, the second to Dev2, and the third to Dev3. However, messages from different lifelines may happen in any order. For example, the second message sent by the actor that goes to Dev2 and the first message sent by Dev1 that goes to the Bus may happen in any order. This mechanism is called weak sequencing. Messages are linked to two message events, one for sending and another for receiving the current message.

Messages can be of three types: asynchronous (open arrow head), synchronous call (closed arrowhead), or reply from a synchronous call (dashed arrow). All messages shown in Figure 2.8 are asynchronous.

Message exchanges can be grouped inside combined fragments that describe operators like parallel composition, conditional, loops, and so on. Figure 2.8 shows a parallel combined fragment PAR, which must be composed of two or more operands, separated by horizontal dashed lines, describing scenarios that can proceed in interleaving. In Figure 2.8, there are three operands, each sending two messages in sequence. For instance, transmitPack(Undecided,1,2) is sent before transmitPack(Undecided,1,3). These messages, however, can be interleaved with those sent in the other operands.

A lifeline can include a state invariant: a constraint on the blocks. If the constraint holds, any message-exchange order just established is a valid scenario of the system, otherwise, it is

**Figure 2.9:** Example of a sequence diagram with *interactionUse*.

Source: Author's ownership.

forbidden. State invariants define properties of the system in terms of the attributes of a block. At the bottom of the lifeline Dev3 in Figure 2.8, there is an invariant Dev3.claim == Undecided, which verifies that the value of the attribute claim of Dev3 is Undecided after it has been turned on and all its packages have been transmitted.

A sequence diagram can include an *interactionUse* element to refer to another sequence diagram, so that part of its definition is provided by the referred diagram. In this way, a diagram can be used several times in the definition of others. For example, Figure 2.9 shows another way of describing the scenario of Figure 2.8 using *interactionUse* elements that refer to the sequence diagram transmitPack, which is shown in Figure 2.10.